PY32L020 Series 32-bit ARM<sup>®</sup> Cortex<sup>®</sup>-M0+ Microcontroller Reference Manual

# **PY32L020 Series**

# 32-bit ARM<sup>®</sup> Cortex<sup>®</sup>-M0+ Microcontroller

# **Reference Manual**

Puya Semiconductor (Shanghai) Co., Ltd.

## Contents

| 1. | Lis  | st of a | bbreviations for registers                | 13 |

|----|------|---------|-------------------------------------------|----|

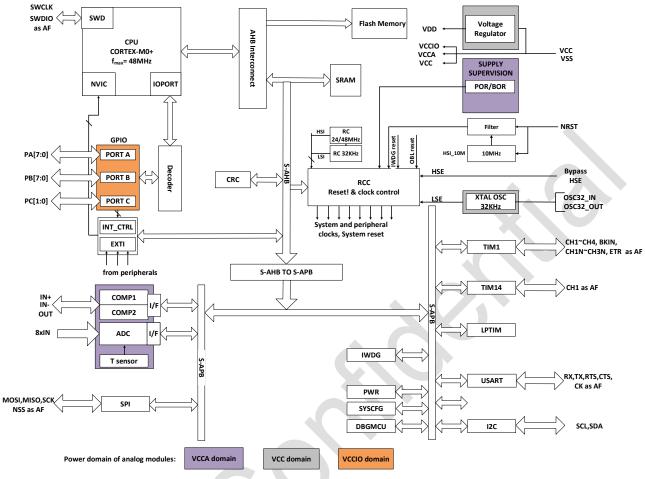

| 2. | Sy   | stem    | block diagram                             | 14 |

| 3. | Ме   | emory   | and bus architecture                      | 15 |

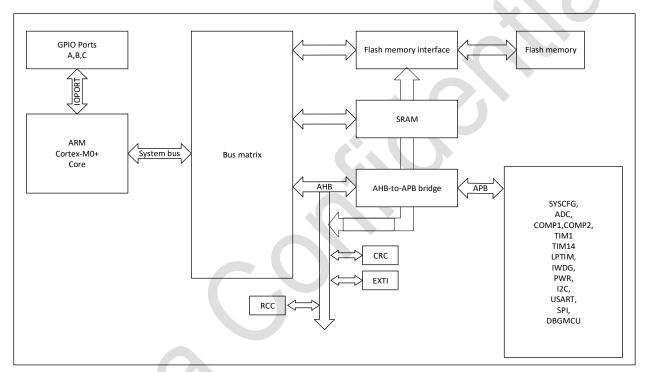

|    | 3.1. | Sys     | tem architecture                          | 15 |

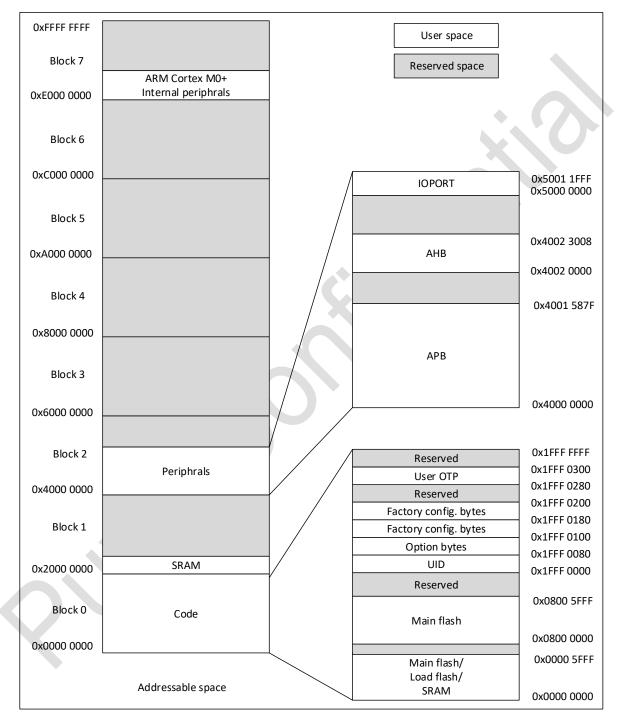

|    | 3.2. | Mer     | nory organization                         | 16 |

|    | 3.3. | Eml     | bedded SRAM                               | 18 |

|    | 3.4. | Flas    | sh memory                                 | 18 |

|    | 3.5. | Boo     | t modes                                   |    |

|    |      | 5.1.    | Memory physical mapping                   |    |

| 4. | En   |         | led Flash memory                          |    |

|    | 4.1. |         | sh main features                          |    |

|    | 4.2. | Flas    | sh memory functional description          |    |

|    | 4.2  | 2.1.    | Flash memory organization                 |    |

|    | 4.2  | 2.2.    | Flash read operation and access latency   |    |

|    | 4.2  | 2.3.    | Flash program and erase operations        |    |

|    | 4.3. |         | que device ID (UID)                       |    |

|    | 4.4. | Flas    | sh option bytes                           |    |

|    | 4.4  | 4.1.    | Flash option byte                         |    |

|    | 4.4  | 4.2.    | Flash option bytes                        |    |

|    | 4.5. | Flas    | sh config bytes                           |    |

|    | 4.5  | 5.1.    | HSI_TRIMMING_FOR_USER                     | 31 |

|    | 4.5  | 5.2.    | HSI_24M/48M_EPPARA0                       |    |

|    | 4.5  | 5.3.    | HSI_24M/48M_EPPARA1                       | 31 |

|    | 4.5  | 5.4.    | HSI_24M/48M_EPPARA2                       | 32 |

|    | 4.5  | 5.5.    | HSI_24M/48M_EPPARA3                       | 32 |

|    | 4.5  | 5.6.    | HSI_24M/48M_EPPARA4                       | 32 |

|    | 4.5  | 5.7.    | LSI_32.768K                               | 32 |

|    | 4.5  | 5.8.    | Flash USER OTP memory bytes               | 32 |

|    | 4.6. | Flas    | sh protection                             | 33 |

|    | 4.6  | 5.1.    | SDK area protection                       | 33 |

|    | 4.6  | 6.2.    | Flash write protection                    | 34 |

|    | 4.6  | 6.3.    | Load flash area protection                | 34 |

|    | 4.6  | 6.4.    | Option byte write protection              | 35 |

|    | 4.7. | Flas    | sh interrupt                              | 35 |

|    | 4.8. | Flas    | sh registers                              | 35 |

|    | 4.8  | 3.1.    | Flash access control register (FLASH_ACR) | 35 |

|    | 4.8  | 3.2.    | Flash key register (Flash_KEYR)           | 35 |

|    | 4.8  | 3.3.    | Flash option key register (Flash_OPTKEYR) | 36 |

|    | 4.8  | 3.4.    | Flash status register (Flash_SR)          | 36 |

|    | 4.8.5.                                                                                                  | Flash control register (FLASH_CR)                                                   | 36                                |

|----|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-----------------------------------|

|    | 4.8.6.                                                                                                  | Flash option register (FLASH_OPTR)                                                  | 38                                |

|    | 4.8.7.                                                                                                  | Flash SDK address register (FLASH_SDKR)                                             | 38                                |

|    | 4.8.8.                                                                                                  | Flash boot control (FLASH_BTCR)                                                     | 39                                |

|    | 4.8.9.                                                                                                  | Flash WRP address register (FLASH_WRPR)                                             | 39                                |

|    | 4.8.10.                                                                                                 | Flash sleep time configuration register (Flash_STCR)                                | 40                                |

|    | 4.8.11.                                                                                                 | Flash TS0 register (FLASH_TS0)                                                      | 40                                |

|    | 4.8.12.                                                                                                 | Flash TS1 register (FLASH_TS1)                                                      | 41                                |

|    | 4.8.13.                                                                                                 | Flash TS2P register (FLASH_TS2P)                                                    | 41                                |

|    | 4.8.14.                                                                                                 | Flash TPS3 register (FLASH_TPS3)                                                    |                                   |

|    | 4.8.15.                                                                                                 | Flash TS3 register (FLASH_TS3)                                                      | 42                                |

|    | 4.8.16.                                                                                                 | Flash PAGE ERASE TPE register (Flash_PERTPE)                                        | 42                                |

|    | 4.8.17.                                                                                                 | Flash SECTOR/MASS ERASE TPE register (FLASH_SMERTPE)                                | 42                                |

|    | 4.8.18.                                                                                                 | Flash PROGRAM TPE register (FLASH_PRGTPE)                                           | 43                                |

|    | 4.8.19.                                                                                                 | Flash PRE-PROGRAM TPE register (FLASH_PRETPE)                                       |                                   |

| 5. |                                                                                                         | ontrol                                                                              |                                   |

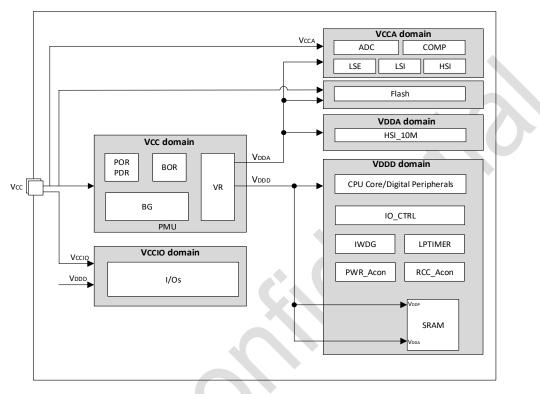

|    | 5.1. Pov                                                                                                | ver supply                                                                          |                                   |

|    | 5.1.1.                                                                                                  | Power supply overview                                                               |                                   |

|    |                                                                                                         | age regulator                                                                       |                                   |

|    | 5.3. Pov                                                                                                | ver monitoring                                                                      | 45                                |

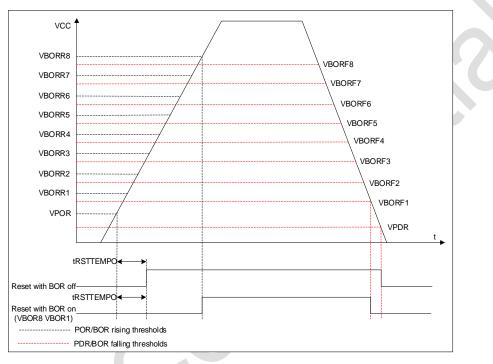

|    |                                                                                                         | Power-on reset (POR) / power-down reset (PDR) / brown-out reset (BOR)               |                                   |

| 6. | -                                                                                                       | wer control                                                                         |                                   |

|    | 6.1. Low                                                                                                | <i>r</i> -power modes                                                               | 46                                |

|    | 6.1.1.                                                                                                  | Introduction                                                                        | 46                                |

|    | 6.1.2.                                                                                                  | Functionalities depending on the working mode                                       | 46                                |

|    | 6.2. Slee                                                                                               | ep mode                                                                             | 47                                |

|    | 6.2.1.                                                                                                  | Entering Sleep mode                                                                 | 47                                |

|    | 6.2.2.                                                                                                  | Exiting Sleep mode                                                                  | 47                                |

|    | 6.3. Sto                                                                                                | o mode                                                                              | 48                                |

|    | 6.3.1.                                                                                                  | Entering Stop mode                                                                  | 48                                |

|    | 6.3.2.                                                                                                  | Exiting Stop mode                                                                   | 48                                |

|    | C 4 D                                                                                                   |                                                                                     |                                   |

|    | 6.4. Rec                                                                                                | luce the system clock frequency                                                     | 49                                |

|    |                                                                                                         | luce the system clock frequency                                                     |                                   |

|    | 6.5. Per                                                                                                |                                                                                     | 49                                |

|    | 6.5. Per                                                                                                | ipheral clock gating                                                                | 49<br>49                          |

| 7. | 6.5. Per<br>6.6. Pov<br>6.6.1.                                                                          | ipheral clock gating                                                                | 49<br>49<br>49                    |

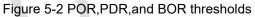

| 7. | 6.5. Peri<br>6.6. Pov<br>6.6.1.<br><b>Reset</b>                                                         | ipheral clock gating<br>ver control registers<br>Power control register 1 (PWR_CR1) | 49<br>49<br>49<br><b>51</b><br>51 |

| 7. | 6.5. Peri<br>6.6. Pov<br>6.6.1.<br><b>Reset</b>                                                         | ipheral clock gating<br>ver control registers<br>Power control register 1 (PWR_CR1) | 49<br>49<br>49<br><b>51</b><br>51 |

| 7. | <ul> <li>6.5. Peri</li> <li>6.6. Pow</li> <li>6.6.1.</li> <li><b>Reset</b></li> <li>7.1. Res</li> </ul> | ipheral clock gating<br>ver control registers<br>Power control register 1 (PWR_CR1) | 49<br>49<br>49<br><b>51</b><br>51 |

|    |    | 7.1.4.  | Watchdog reset                                                   | . 52 |

|----|----|---------|------------------------------------------------------------------|------|

|    |    | 7.1.5.  | Software reset                                                   | .52  |

|    |    | 7.1.6.  | Option byte loader reset                                         | .52  |

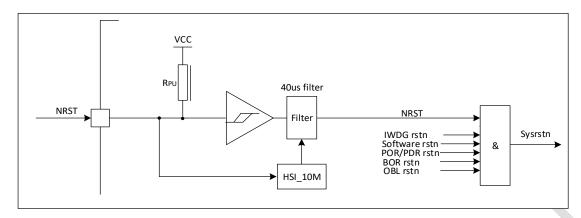

| 8. |    | Clocks  |                                                                  | .53  |

|    | 8. | 1. Clo  | ock sources                                                      | .53  |

|    |    | 8.1.1.  | External high speed clock (HSE bypass)                           | .53  |

|    |    | 8.1.2.  | External low speed clock LSE                                     | .53  |

|    |    | 8.1.3.  | External clock source (LSE bypass)                               | .53  |

|    |    | 8.1.4.  | Internal high-speed clock HSI                                    | .53  |

|    |    | 8.1.5.  | Internal low speed clock LSI                                     |      |

|    | 8. |         | ock tree                                                         |      |

|    | 8. | 3. Clo  | ock security system (CSS)                                        | .54  |

|    | 8. |         | Itput clock                                                      |      |

|    | 8. | 5. Clo  | ock calibration                                                  |      |

|    |    | 8.5.1.  | HSI Calibration                                                  |      |

|    |    | 8.5.2.  | LSI calibration                                                  |      |

|    | 8. | 6. Re   | set/clock register                                               |      |

|    |    | 8.6.1.  | Clock control register (RCC_CR)                                  | .56  |

|    |    | 8.6.2.  | Internal clock sources calibration register (RCC_ICSCR)          | .57  |

|    |    | 8.6.3.  | Clock configuration register (RCC_CFGR)                          | .58  |

|    |    | 8.6.4.  | External clock sources control register (RCC_ECSCR)              | .59  |

|    |    | 8.6.5.  | Clock interrupt enable register (RCC_CIER)                       | .60  |

|    |    | 8.6.6.  | Clock interrupt flag register (RCC_CIFR)                         | .60  |

|    |    | 8.6.7.  | Clock interrupt clear register (RCC_CICR)                        | .61  |

|    |    | 8.6.8.  | I/O port reset register (RCC_IOPRSTR)                            | .61  |

|    |    | 8.6.9.  | AHB peripheral reset register (RCC_AHBRSTR)                      | .62  |

|    |    | 8.6.10. | APB peripheral reset register 1 (RCC_APBRSTR1)                   | .62  |

|    |    | 8.6.11. | APB peripheral reset register 2 (RCC_APBRSTR2)                   | .62  |

|    |    | 8.6.12. | I/O port clock enable register (RCC_IOPENR)                      | .63  |

|    |    | 8.6.13. | AHB peripheral clock enable register (RCC_AHBENR)                | .63  |

|    |    | 8.6.14. | APB peripheral clock enable register 1 (RCC_APBENR1)             | .64  |

|    |    | 8.6.15. | APB peripheral clock enable register 2(RCC_APBENR2)              | .64  |

|    |    | 8.6.16. | Peripherals independent clock configuration register (RCC_CCIPR) | .65  |

|    |    | 8.6.17. | RCC domain control register (RCC_BDCR)                           | .66  |

|    |    | 8.6.18. | Control/status register (RCC_CSR)                                | .66  |

| 9. |    | Genera  | Il-purpose I/Os (GPIO)                                           | .68  |

|    | 9. | 1. Int  | roduction                                                        | .68  |

|    | 9. | 2. GF   | PIO main features                                                | .68  |

|    | 9. | 3. GF   | PIO functional description                                       | .68  |

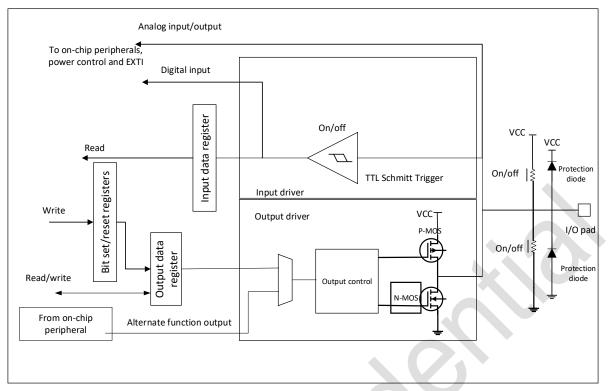

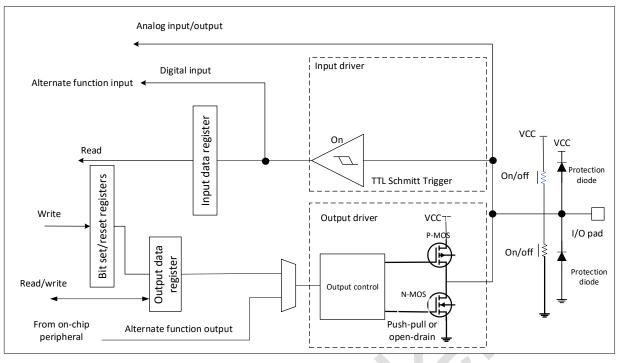

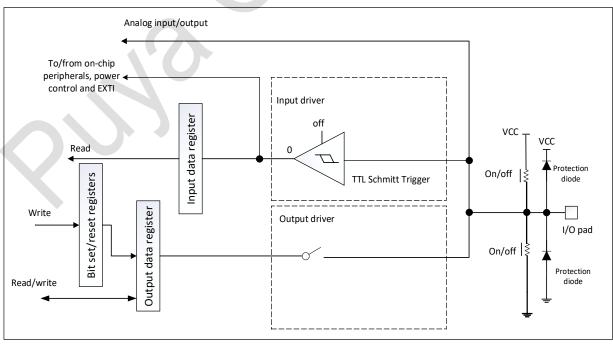

|    |    | 9.3.1.  | General-purpose I/Os (GPIO)                                      | .69  |

| 9.3.2.    | I/O pin alternate function multiplexer and mapping               | 69 |

|-----------|------------------------------------------------------------------|----|

| 9.3.3.    | I/O port control registers                                       | 70 |

| 9.3.4.    | I/O port data registers                                          | 70 |

| 9.3.5.    | I/O data bitwise handling                                        | 70 |

| 9.3.6.    | GPIO locking mechanism                                           | 71 |

| 9.3.7.    | I/O alternate function input/output                              | 71 |

| 9.3.8.    | External interrupt/wakeup lines                                  | 71 |

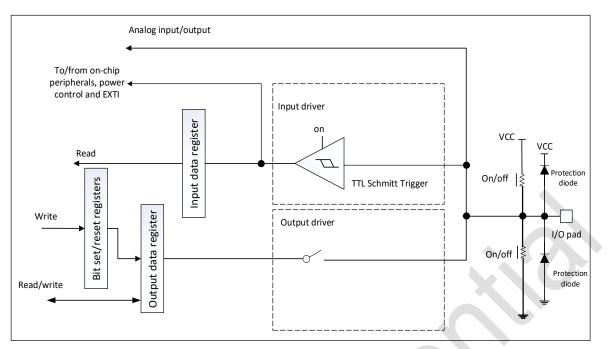

| 9.3.9.    | Input configuration                                              | 71 |

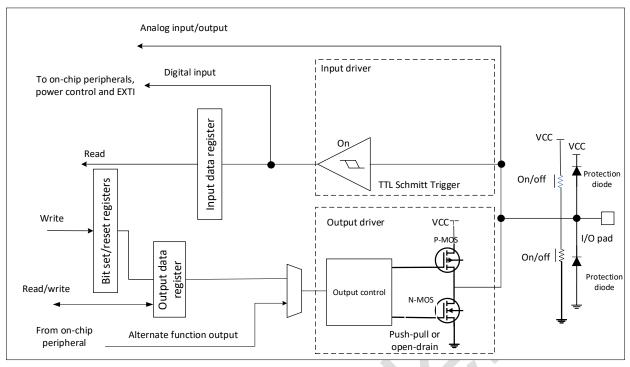

| 9.3.10.   | Output configuration                                             | 72 |

| 9.3.11.   |                                                                  | 73 |

| 9.3.12.   | 5 5                                                              |    |

| 9.3.13.   | 5                                                                |    |

| 9.4. GI   | PIO registers                                                    |    |

| 9.4.1.    | GPIO port mode register (GPIOx_MODER)(x =A, B, C)                |    |

| 9.4.2.    | GPIO port output type register (GPIOx_OTYPER) (x = A, B, C)      | 75 |

| 9.4.3.    | GPIO port output speed register (GPIOx_OSPEEDR) (x = A, B, C)    | 76 |

| 9.4.4.    | GPIO port pull-up/pull-down register (GPIOx_PUPDR) (x = A, B, C) | 76 |

| 9.4.5.    | GPIO port input data register (GPIOx_IDR) (x = A, B, C)          | 77 |

| 9.4.6.    | GPIO port output data register (GPIOx_ODR) (x = A, B, C)         |    |

| 9.4.7.    | GPIO port bit set/reset register (GPIOx_BSRR) (x = A, B, C)      | 77 |

| 9.4.8.    | GPIO port configuration lock register (GPIOx_LCKR) (x = A, B, C) | 78 |

| 9.4.9.    | GPIO alternate function low register (GPIOx_AFRL) (x = A, B, C)  | 78 |

| 9.4.10.   | GPIO port bit set/reset register (GPIOx_BSRR) (x = A, B, C)      | 80 |

| -         | em configuration controller (SYSCFG)                             |    |

| 10.1.     | SYSCFG registers                                                 | 81 |

| 10.1.1.   |                                                                  |    |

| 10.1.2.   |                                                                  |    |

| 10.1.3.   | GPIO filter enable (GPIO_ENS)                                    | 82 |

| 11. Inter | rupts and events                                                 | 83 |

| 11.1.     | Nested vectored interrupt controller (NVIC)                      |    |

| 11.1.1.   | Main features                                                    | 83 |

| 11.1.2.   | SysTick calibration value register                               | 83 |

| 11.1.3.   | Interrupt and exception vectors                                  |    |

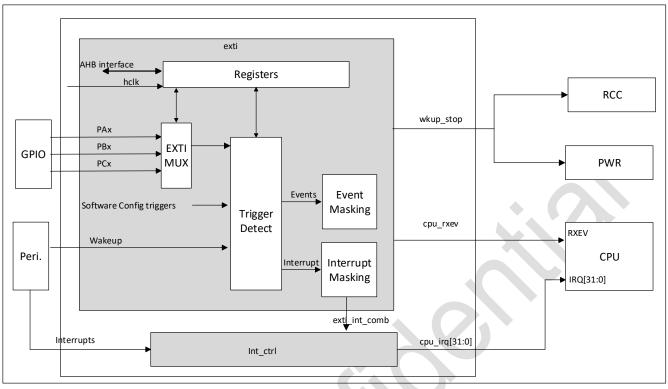

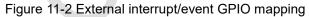

| 11.2.     | Extended interrupts and events controller (EXTI)                 |    |

| 11.2.1.   | EXTI main features                                               | 84 |

| 11.2.2.   | EXTI block diagram                                               | 85 |

| 11.2.3.   | EXTI configurable event trigger wake-up                          | 85 |

| 11.2.4.   | EXTI direct event input wake-up                                  |    |

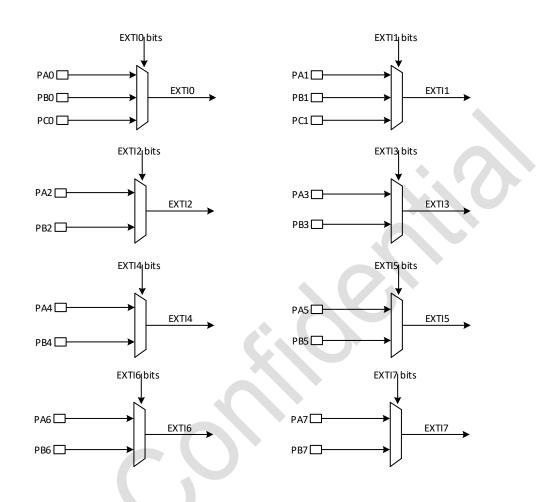

| 11.2.5.   | •                                                                |    |

| 11.3.     | EXTI register                                                    | 87 |

| 11.3.1.  | EXTI rising trigger selection register (EXTI_RTSR)                    | 87  |

|----------|-----------------------------------------------------------------------|-----|

| 11.3.2.  | EXTI falling trigger selection register (EXTI_FTSR)                   |     |

| 11.3.3.  | Software interrupt event register (EXTI_SWIER)                        |     |

| 11.3.4.  | Pending register (EXTI_PR)                                            |     |

| 11.3.5.  | EXTI external interrupt selection register 1 (EXTI_EXTICR1)           | 91  |

| 11.3.6.  | EXTI external interrupt selection register 2 (EXTI_EXTICR2)           | 91  |

| 11.3.7.  | Interrupt mask register (EXTI_IMR)                                    | 92  |

| 11.3.8.  | Event mask register (EXTI_EMR)                                        | 92  |

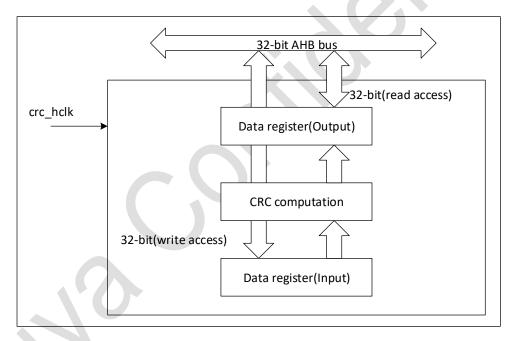

| 12. Cycl | c redundancy check (CRC)                                              | 94  |

|          | ntroduction                                                           |     |

|          | CRC main features                                                     |     |

| 12.3.    | CRC functional description                                            |     |

|          | CRC block diagram                                                     |     |

| 12.4.    | CRC registers                                                         |     |

| 12.4.1.  | CRC data register (CRC_DR)                                            | 95  |

| 12.4.2.  | CRC independent data register (CRC_IDR)                               |     |

| 12.4.3.  | CRC control register (CRC_CR)                                         | 95  |

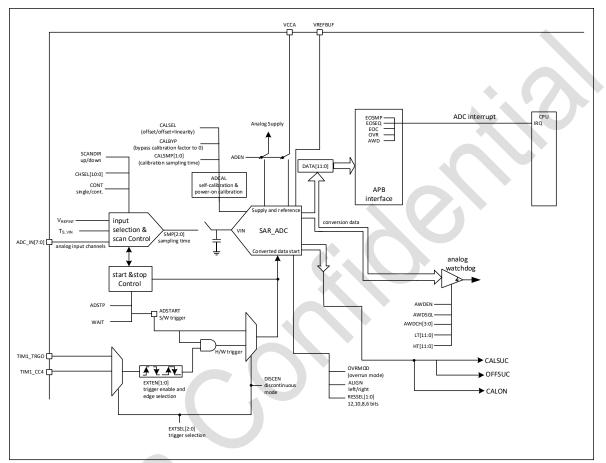

|          | og-to-digital converters (ADC)                                        |     |

| 13.1.    | ntroduction                                                           |     |

| 13.2.    | ADC main features                                                     |     |

| 13.3.    | ADC functional description                                            |     |

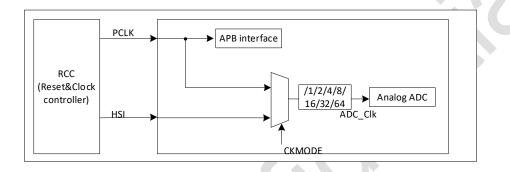

| 13.3.1.  | ADC block diagram                                                     |     |

| 13.3.2.  | Calibration (ADCAL)                                                   |     |

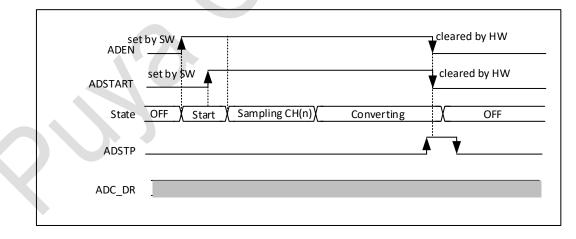

| 13.3.3.  | ADC on-off control (ADEN)                                             |     |

| 13.3.4.  | ADC clock                                                             |     |

| 13.3.5.  | Configuring the ADC                                                   | 100 |

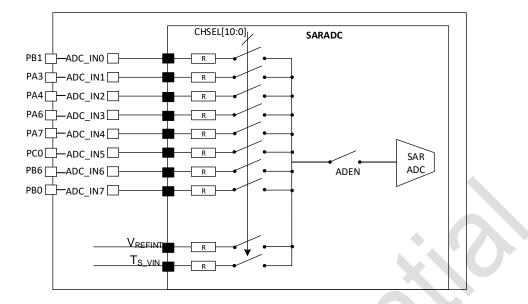

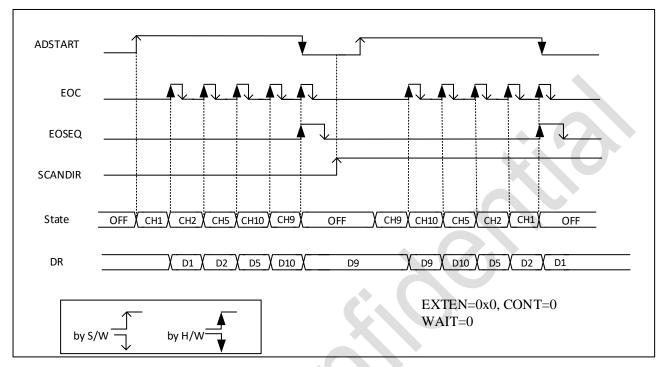

| 13.3.6.  | Channel selection (CHSEL, SCANDIR)                                    | 100 |

| 13.3.7.  | Programmable sampling time (SMP)                                      | 100 |

| 13.3.8.  | Single conversion mode (CONT = 0, DISCEN = 0)                         | 101 |

| 13.3.9.  | Continuous conversion mode (CONT=1)                                   | 101 |

| 13.3.10  | . Discontinuous conversion mode (DISCEN = 1)                          | 101 |

| 13.3.11  | . Starting conversions (ADSTART)                                      | 102 |

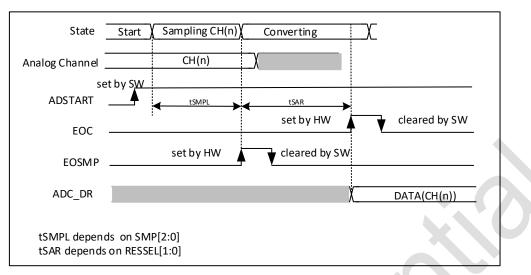

| 13.3.12  | ADC timing                                                            | 102 |

| 13.3.13  | . Stopping an ongoing conversion (ADSTP)                              | 103 |

| 13.3.14  | . Conversion on external trigger and trigger polarity (EXTSEL, EXTEN) |     |

| 13.3.15  | . Quick transition mode                                               | 104 |

| 13.3.16  | . End of conversion / end of sampling phase                           | 104 |

| 13.3.17  | . End of conversion sequence (EOSEQ flag)                             | 104 |

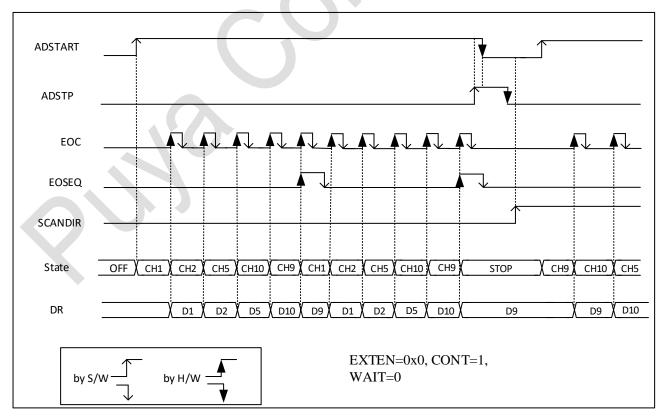

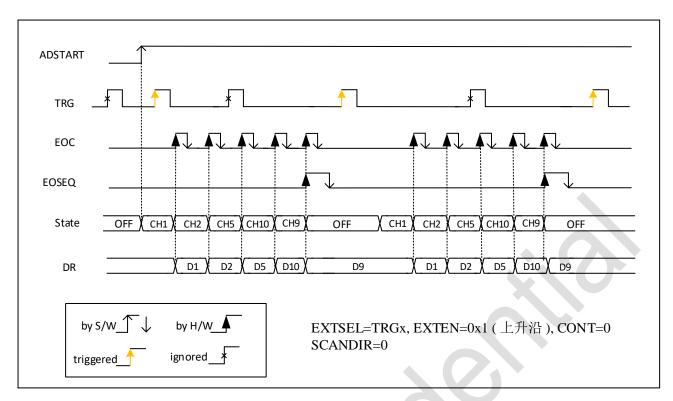

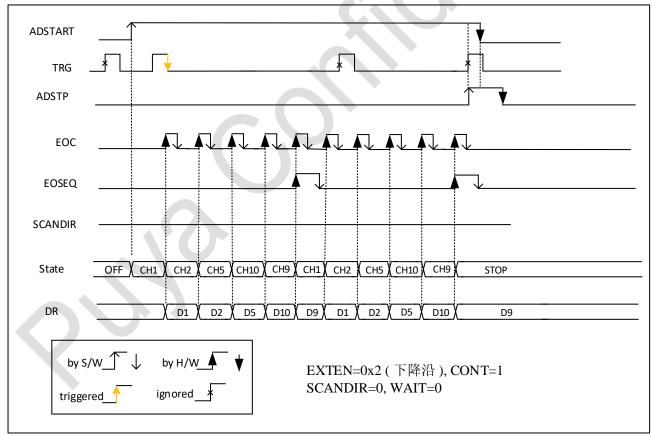

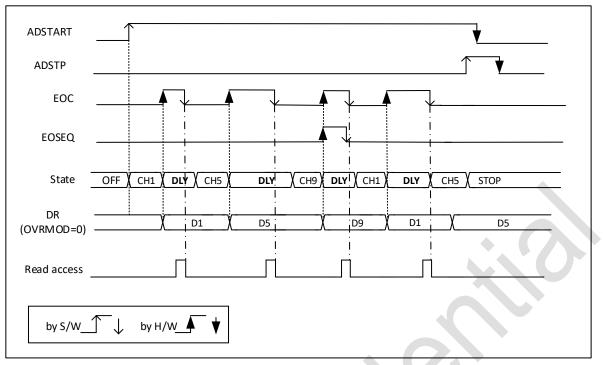

| 13.3.18  | . Example timing diagrams                                             | 105 |

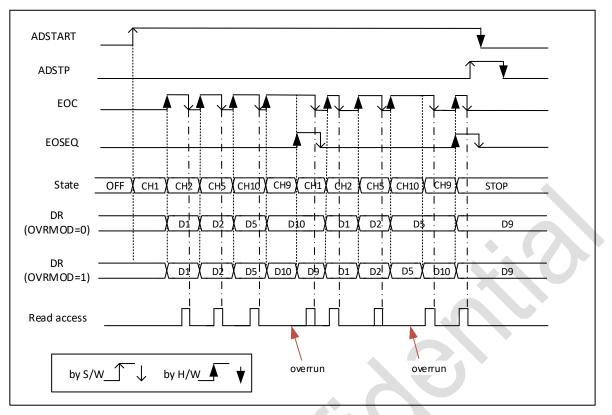

| 13.3.19  | Data management                                                       | 107 |

| 13.3.20. | Low-power features                                           | 108 |

|----------|--------------------------------------------------------------|-----|

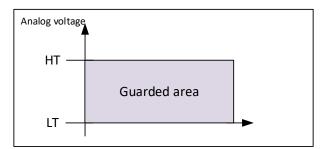

| 13.3.21. | Analog watchdog                                              | 109 |

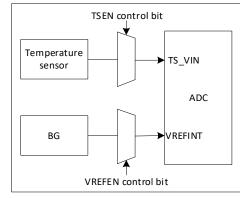

| 13.3.22. | Temperature sensor and internal reference voltage            | 110 |

| 13.3.23. | ADC interrupts                                               | 112 |

| 13.4. A  | DC registers                                                 | 112 |

| 13.4.1.  | ADC interrupt and status register (ADC_ISR)                  | 112 |

| 13.4.2.  | ADC interrupt enable register (ADC_IER)                      | 113 |

| 13.4.3.  | ADC control register (ADC_CR)                                | 114 |

| 13.4.4.  | ADC configuration register 1 (ADC_CFGR1)                     | 115 |

| 13.4.5.  | ADC configuration register 2 (ADC_CFGR2)                     | 117 |

| 13.4.6.  | ADC sampling time register (ADC_SMPR)                        |     |

| 13.4.7.  | ADC watchdog threshold register (ADC_TR)                     | 118 |

| 13.4.8.  | ADC channel selection register (ADC_CHSELR)                  |     |

| 13.4.9.  | ADC data register (ADC_DR)                                   | 119 |

| 13.4.10. | ADC calibration configuration and status register (ADC_CCSR) |     |

| 13.4.11. | ADC common configuration register (ADC_CCR)                  |     |

|          | arator (COMP)                                                |     |

|          | troduction                                                   |     |

|          | OMP main features                                            |     |

| 14.3. C  | OMP functional description                                   |     |

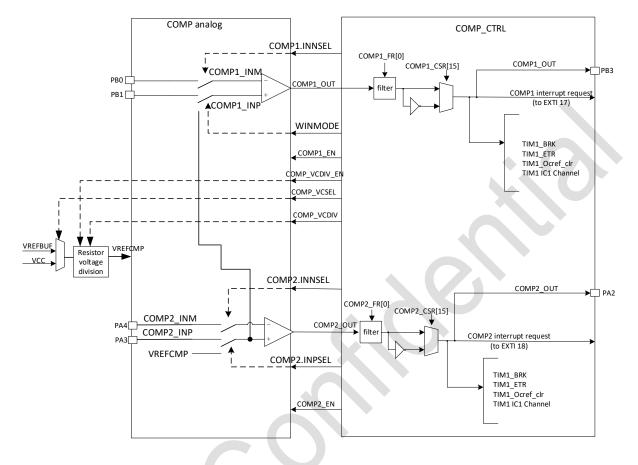

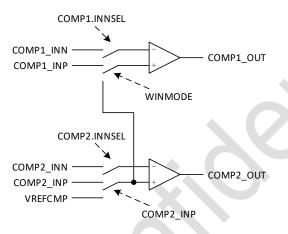

| 14.3.1.  | COMP block diagram                                           |     |

| 14.3.2.  | COMP pins and internal signals                               |     |

| 14.3.3.  | COMP reset and clocks                                        | 122 |

| 14.3.4.  | Window comparator                                            |     |

| 14.3.5.  | Low-power modes                                              |     |

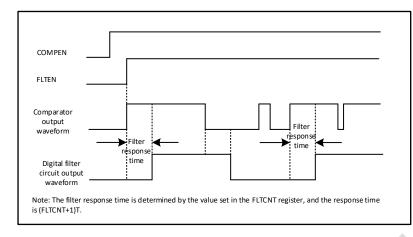

| 14.3.6.  | Comparator filtering                                         |     |

| 14.3.7.  | COMP interrupts                                              |     |

| 14.3.8.  | COMP select V <sub>REFCMP</sub> configuration                |     |

|          | OMP registers                                                |     |

|          | Comparator 1 control and status register (COMP1_CSR)         |     |

| 14.4.2.  | Comparator 1 filtering register (COMP1_FR)                   |     |

| 14.4.3.  | Comparator 2 control and status register (COMP2_CSR)         |     |

|          | Comparator 2 filtering register (COMP2_FR)                   |     |

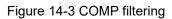

|          | nced-control timers (TIM1)                                   |     |

|          | IM1 introduction                                             |     |

|          | IM1 main features                                            |     |

|          | IM1 functional description                                   |     |

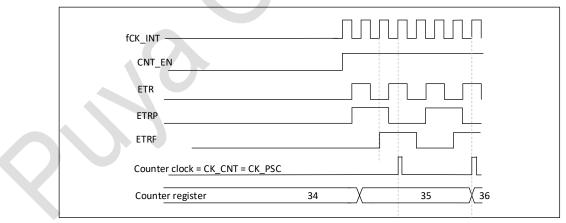

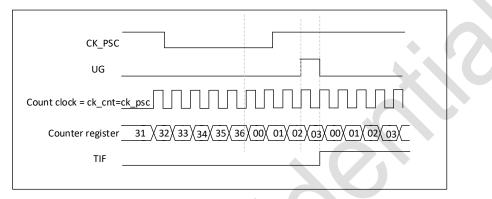

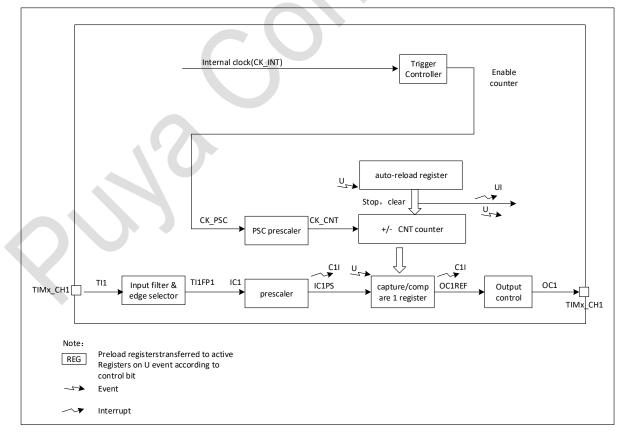

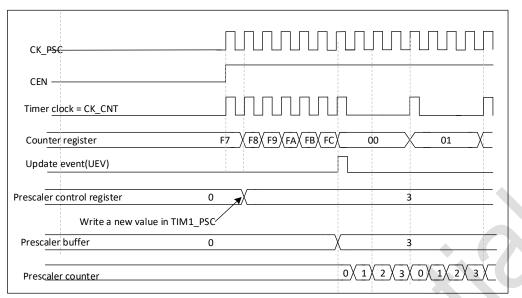

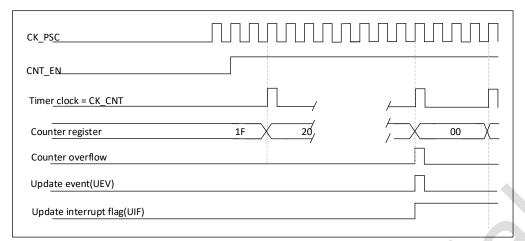

| 15.3.1.  | Time-base unit                                               |     |

| 15.3.2.  | Timer enable                                                 |     |

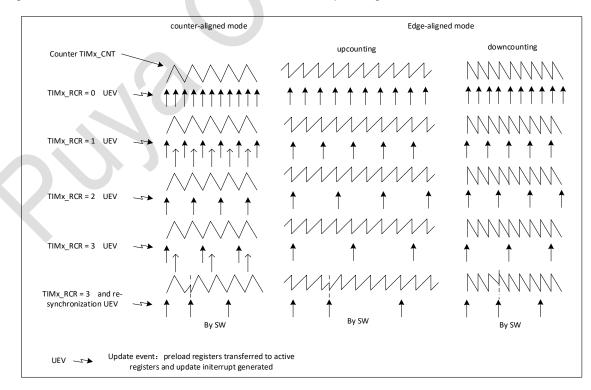

| 15.3.3.  | Repetition counter                                           | 139 |

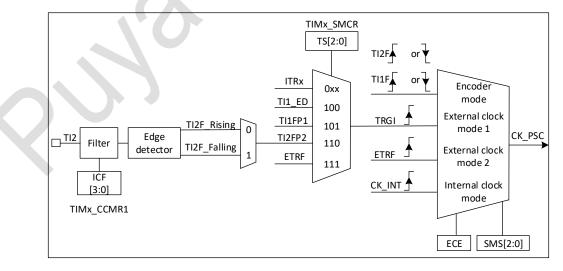

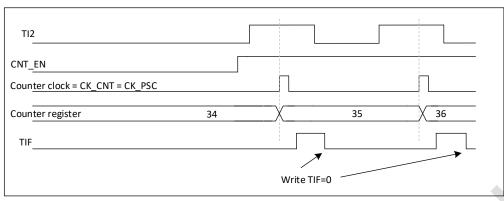

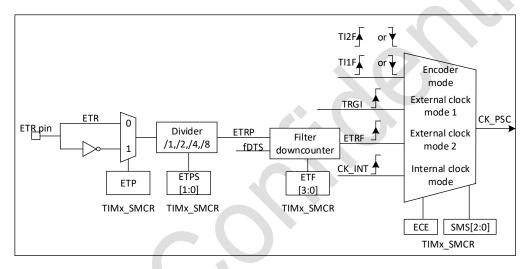

| 15.3.4.  | Clock sources                                     | 140 |

|----------|---------------------------------------------------|-----|

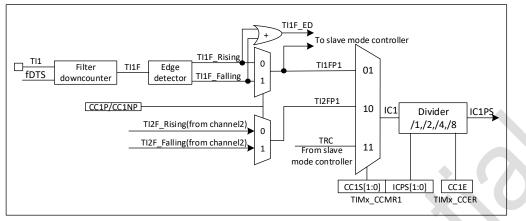

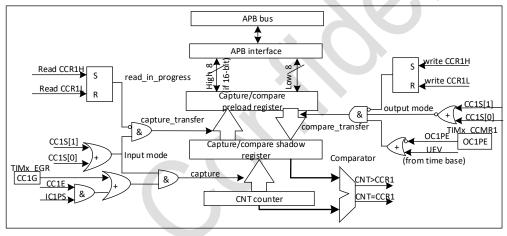

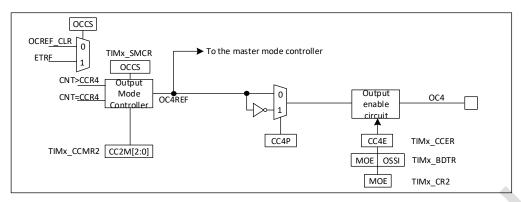

| 15.3.5.  | Capture/Compare channels                          | 141 |

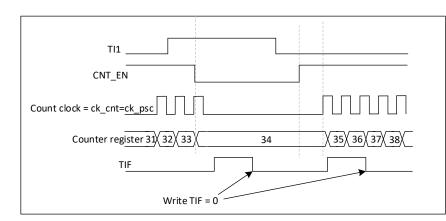

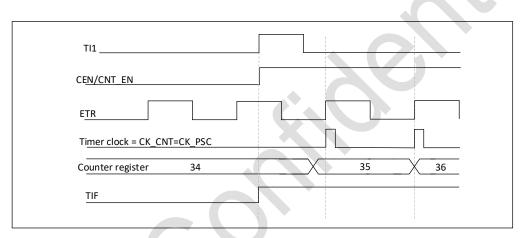

| 15.3.6.  | Input capture mode:                               | 143 |

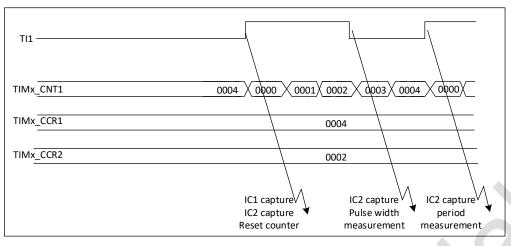

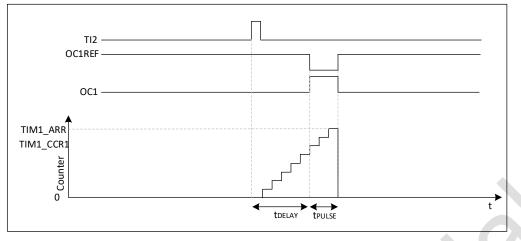

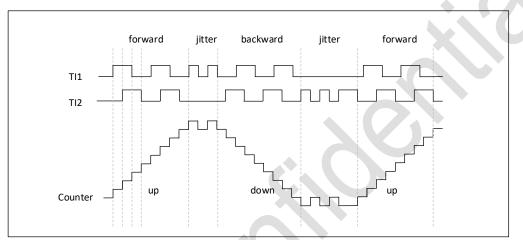

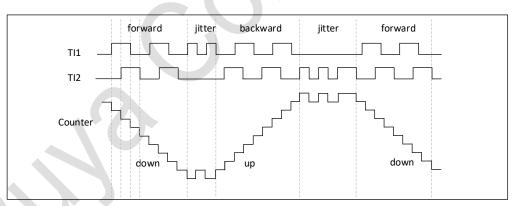

| 15.3.7.  | PWM input mode                                    | 144 |

| 15.3.8.  | Forced output mode                                | 145 |

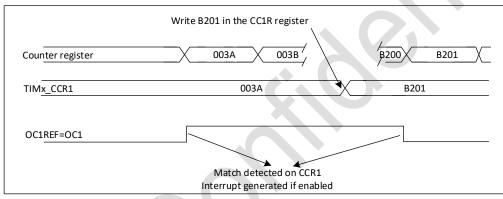

| 15.3.9.  | Output compare mode                               | 145 |

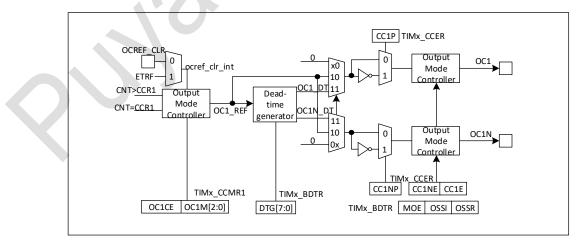

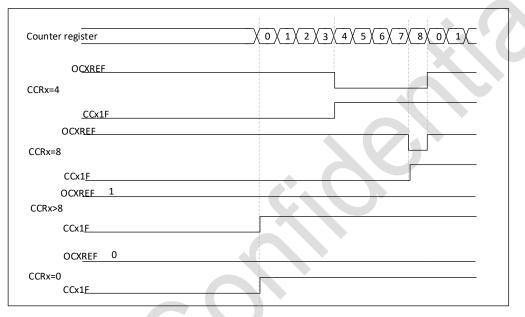

| 15.3.10. | PWM mode                                          | 146 |

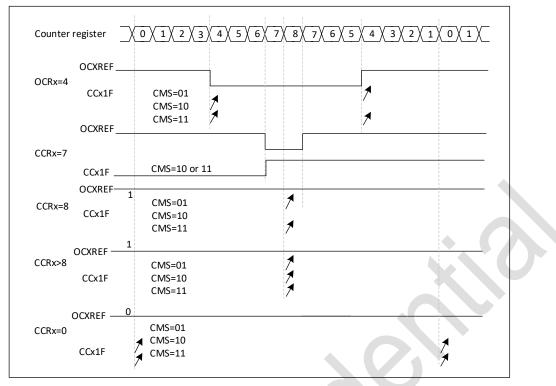

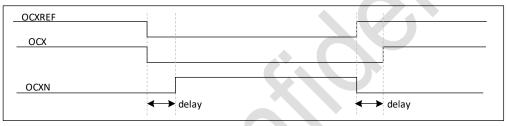

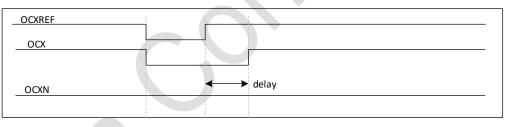

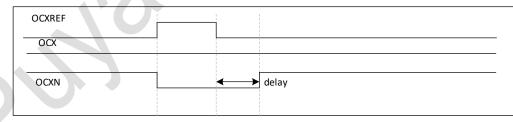

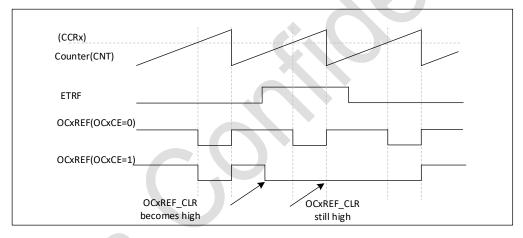

| 15.3.11. | Complementary outputs and dead-time insertion     | 148 |

| 15.3.12. | Using the break function                          | 150 |

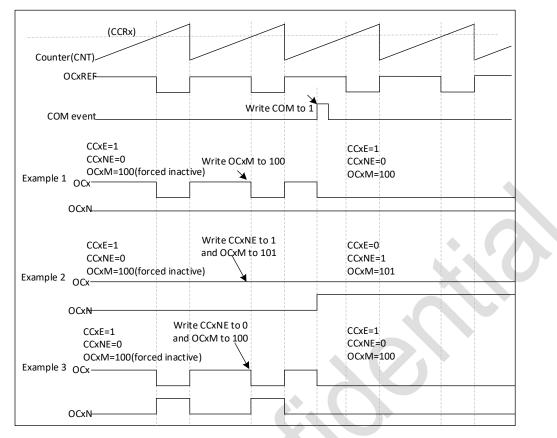

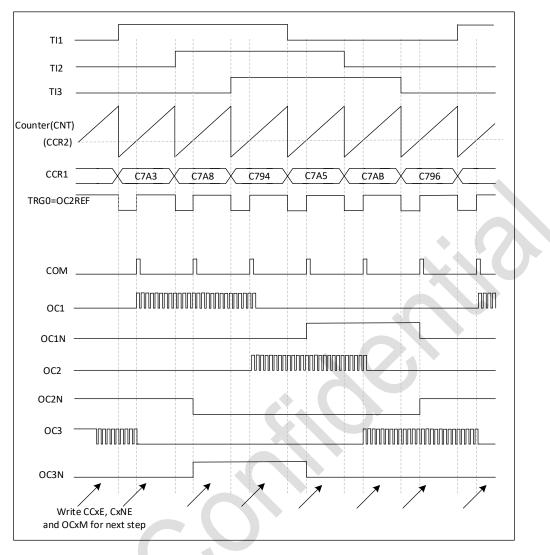

| 15.3.13. | 5                                                 | 152 |

| 15.3.14. |                                                   |     |

| 15.3.15. |                                                   |     |

| 15.3.16. |                                                   |     |

| 15.3.17. |                                                   |     |

| 15.3.18. | 5                                                 |     |

| 15.3.19. | 55 <i>,</i>                                       |     |

| 15.3.20. | 5                                                 |     |

| 15.4. T  | IM1 registers                                     |     |

| 15.4.1.  | TIM1 control register 1 (TIM1_CR1)                |     |

| 15.4.2.  | TIM1 control register 2 (TIM1_CR2)                |     |

| 15.4.3.  | TIM1 slave mode control register (TIM1_SMCR)      |     |

| 15.4.4.  | TIM1 Interrupt enable register (TIM1_DIER)        |     |

| 15.4.5.  | TIM1 status register (TIM1_SR)                    |     |

| 15.4.6.  | TIM1 event generation register (TIM1_EGR)         |     |

| 15.4.7.  | TIM1 capture/compare mode register 1 (TIM1_CCMR1) | 168 |

| 15.4.8.  | TIM1 capture/compare mode register 2 (TIM1_CCMR2) | 171 |

| 15.4.9.  | TIM1 capture/compare enable register (TIM1_CCER)  | 172 |

| 15.4.10. |                                                   |     |

| 15.4.11. | TIM1 prescaler register (TIM1_PSC)                | 174 |

| 15.4.12. | TIM1 auto-reload register (TIM1_ARR)              | 174 |

| 15.4.13. | TIM1 Repetition counter register (TIM1_RCR)       | 175 |

| 15.4.14. | TIM1 capture/compare register 1 (TIM1_CCR1)       | 175 |

| 15.4.15. | TIM1 capture/compare register 2 (TIM1_CCR2)       | 176 |

| 15.4.16. | TIM1 capture/compare register 3 (TIM1_CCR3)       | 176 |

| 15.4.17. | TIM1 capture/compare register 4 (TIM1_CCR4)       | 176 |

| 15.4.18. | TIM1 break and dead-time register (TIM1_BDTR)     | 177 |

|          | ral-purpose timer (TIM14)                         |     |

|          | IM14 introduction                                 |     |

| 16.2. T  | IM14 main features                                | 179 |

| 16.3. T  | IM14 functional description                       |     |

| 16.3.1.                                                                                                                                                                                                                                                                                                                                                                                      | Time-base unit                                                                                                                                                                                                                                                                                                                                                                                                   | 180                                                                                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

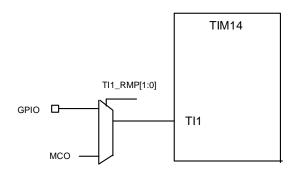

| 16.3.2.                                                                                                                                                                                                                                                                                                                                                                                      | Clock sources                                                                                                                                                                                                                                                                                                                                                                                                    | 184                                                                                                                                      |

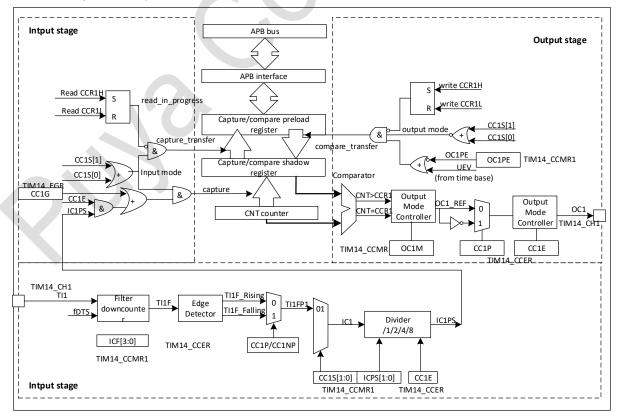

| 16.3.3.                                                                                                                                                                                                                                                                                                                                                                                      | Capture/Compare channels                                                                                                                                                                                                                                                                                                                                                                                         | 184                                                                                                                                      |

| 16.3.4.                                                                                                                                                                                                                                                                                                                                                                                      | Input capture mode:                                                                                                                                                                                                                                                                                                                                                                                              | 185                                                                                                                                      |

| 16.3.5.                                                                                                                                                                                                                                                                                                                                                                                      | Forced output mode                                                                                                                                                                                                                                                                                                                                                                                               | 186                                                                                                                                      |

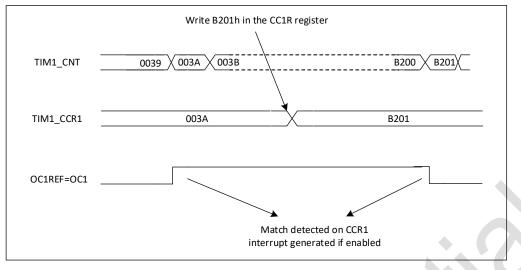

| 16.3.6.                                                                                                                                                                                                                                                                                                                                                                                      | Output compare mode                                                                                                                                                                                                                                                                                                                                                                                              | 186                                                                                                                                      |

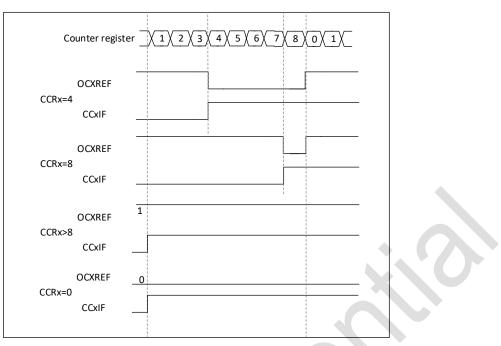

| 16.3.7.                                                                                                                                                                                                                                                                                                                                                                                      | PWM mode                                                                                                                                                                                                                                                                                                                                                                                                         | 187                                                                                                                                      |

| 16.3.8.                                                                                                                                                                                                                                                                                                                                                                                      | Timer synchronization                                                                                                                                                                                                                                                                                                                                                                                            | 188                                                                                                                                      |

| 16.3.9.                                                                                                                                                                                                                                                                                                                                                                                      | Debug mode                                                                                                                                                                                                                                                                                                                                                                                                       | . 188                                                                                                                                    |

| 16.4. T                                                                                                                                                                                                                                                                                                                                                                                      | IM14 registers                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                          |

| 16.4.1.                                                                                                                                                                                                                                                                                                                                                                                      | TIM14 control register 1 (TIM14_CR1)                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                          |

| 16.4.2.                                                                                                                                                                                                                                                                                                                                                                                      | TIM14 Interrupt enable register (TIM14_DIER)                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                          |

| 16.4.3.                                                                                                                                                                                                                                                                                                                                                                                      | TIM14 status register (TIM14_SR)                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                          |

| 16.4.4.                                                                                                                                                                                                                                                                                                                                                                                      | TIM14 event generation register (TIM14_EGR)                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                          |

| 16.4.5.                                                                                                                                                                                                                                                                                                                                                                                      | TIM14 capture/compare mode register 1 (TIM14_CCMR1)                                                                                                                                                                                                                                                                                                                                                              | 191                                                                                                                                      |

| 16.4.6.                                                                                                                                                                                                                                                                                                                                                                                      | TIM14 capture/compare enable register (TIM14_CCER)                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                          |

| 16.4.7.                                                                                                                                                                                                                                                                                                                                                                                      | TIM14 counter (TIM14_CNT)                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                          |

| 16.4.8.                                                                                                                                                                                                                                                                                                                                                                                      | TIM14 prescaler (TIM14_PSC)                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                          |

| 16.4.9.                                                                                                                                                                                                                                                                                                                                                                                      | TIM14 auto-reload register (TIM14_ARR)                                                                                                                                                                                                                                                                                                                                                                           | 194                                                                                                                                      |

| 16.4.10.                                                                                                                                                                                                                                                                                                                                                                                     | TIM14 capture/compare register 1 (TIM14_CCR1)                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                          |

| 16.4.11.                                                                                                                                                                                                                                                                                                                                                                                     | TIM14 option register (TIM14_OR)                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                          |

| 17. Low-µ                                                                                                                                                                                                                                                                                                                                                                                    | oower timer (LPTIM)                                                                                                                                                                                                                                                                                                                                                                                              | 196                                                                                                                                      |

| 17. Low-µ                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                  | 196                                                                                                                                      |

| 17. Low-µ<br>17.1. lı                                                                                                                                                                                                                                                                                                                                                                        | oower timer (LPTIM)                                                                                                                                                                                                                                                                                                                                                                                              | <b>196</b><br>196                                                                                                                        |

| 17. Low-µ<br>17.1. lı<br>17.2. L                                                                                                                                                                                                                                                                                                                                                             | oower timer (LPTIM)                                                                                                                                                                                                                                                                                                                                                                                              | <b> 196</b><br>196<br>196                                                                                                                |

| 17. Low-µ<br>17.1. lı<br>17.2. L                                                                                                                                                                                                                                                                                                                                                             | oower timer (LPTIM)<br>htroduction<br>PTIM main features                                                                                                                                                                                                                                                                                                                                                         | <b>196</b><br>196<br>196<br>196                                                                                                          |

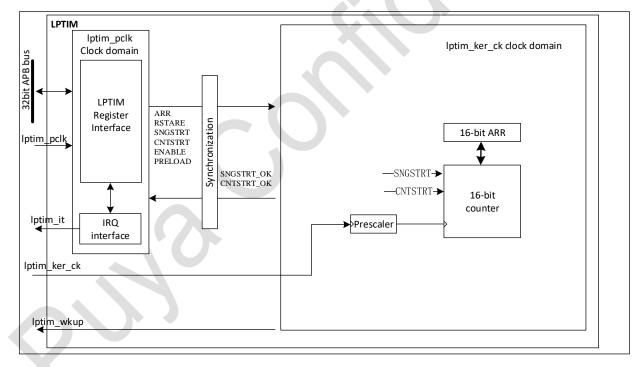

| 17. Low-p<br>17.1. lı<br>17.2. L<br>17.3. L                                                                                                                                                                                                                                                                                                                                                  | bower timer (LPTIM)<br>Introduction<br>PTIM main features<br>PTIM functional description<br>LPTIM block diagram<br>LPTIM reset and clocks                                                                                                                                                                                                                                                                        | 196<br>196<br>196<br>196<br>196<br>196                                                                                                   |

| 17. Low-r<br>17.1. li<br>17.2. L<br>17.3. L<br>17.3.1.                                                                                                                                                                                                                                                                                                                                       | bower timer (LPTIM)<br>htroduction<br>PTIM main features<br>PTIM functional description<br>LPTIM block diagram                                                                                                                                                                                                                                                                                                   | 196<br>196<br>196<br>196<br>196<br>196                                                                                                   |

| 17. Low-p<br>17.1. li<br>17.2. L<br>17.3. L<br>17.3.1.<br>17.3.2.                                                                                                                                                                                                                                                                                                                            | power timer (LPTIM)         introduction         PTIM main features         PTIM functional description         LPTIM block diagram         LPTIM reset and clocks         Prescaler         Operating mode                                                                                                                                                                                                      | 196<br>196<br>196<br>196<br>196<br>196<br>197<br>197                                                                                     |

| <ul> <li>17. Low-F</li> <li>17.1. In</li> <li>17.2. L</li> <li>17.3. L</li> <li>17.3.1.</li> <li>17.3.2.</li> <li>17.3.3.</li> </ul>                                                                                                                                                                                                                                                         | bower timer (LPTIM)<br>Introduction<br>PTIM main features<br>PTIM functional description<br>LPTIM block diagram<br>LPTIM reset and clocks<br>Prescaler                                                                                                                                                                                                                                                           | 196<br>196<br>196<br>196<br>196<br>196<br>197<br>197                                                                                     |

| 17. Low-F<br>17.1. II<br>17.2. L<br>17.3. L<br>17.3.1.<br>17.3.2.<br>17.3.3.<br>17.3.4.                                                                                                                                                                                                                                                                                                      | power timer (LPTIM)         introduction         PTIM main features         PTIM functional description         LPTIM block diagram         LPTIM reset and clocks         Prescaler         Operating mode                                                                                                                                                                                                      | 196<br>196<br>196<br>196<br>196<br>196<br>197<br>197<br>197                                                                              |

| <ul> <li>17. Low-F</li> <li>17.1. In</li> <li>17.2. L</li> <li>17.3. L</li> <li>17.3.1.</li> <li>17.3.2.</li> <li>17.3.3.</li> <li>17.3.4.</li> <li>17.3.5.</li> </ul>                                                                                                                                                                                                                       | bower timer (LPTIM)<br>Introduction<br>PTIM main features<br>PTIM functional description<br>LPTIM block diagram<br>LPTIM reset and clocks<br>Prescaler<br>Operating mode<br>Register update                                                                                                                                                                                                                      | 196<br>196<br>196<br>196<br>196<br>196<br>197<br>197<br>197<br>198                                                                       |

| <ul> <li>17. Low-F</li> <li>17.1. In</li> <li>17.2. L</li> <li>17.3. L</li> <li>17.3.1.</li> <li>17.3.2.</li> <li>17.3.3.</li> <li>17.3.4.</li> <li>17.3.6.</li> <li>17.3.7.</li> <li>17.3.8.</li> </ul>                                                                                                                                                                                     | bower timer (LPTIM)<br>Introduction<br>PTIM main features<br>PTIM functional description<br>LPTIM block diagram<br>LPTIM reset and clocks<br>Prescaler<br>Operating mode<br>Register update<br>Timer enable.<br>Timer counter reset<br>Debug mode                                                                                                                                                                | 196<br>196<br>196<br>196<br>196<br>196<br>197<br>197<br>197<br>198<br>198<br>198                                                         |

| <ul> <li>17. Low-F</li> <li>17.1. In</li> <li>17.2. L</li> <li>17.3. L</li> <li>17.3.1.</li> <li>17.3.2.</li> <li>17.3.3.</li> <li>17.3.4.</li> <li>17.3.6.</li> <li>17.3.7.</li> <li>17.3.8.</li> </ul>                                                                                                                                                                                     | bower timer (LPTIM)<br>htroduction<br>PTIM main features<br>PTIM functional description<br>LPTIM block diagram<br>LPTIM reset and clocks<br>Prescaler<br>Operating mode<br>Register update<br>Timer enable<br>Timer counter reset                                                                                                                                                                                | 196<br>196<br>196<br>196<br>196<br>196<br>197<br>197<br>197<br>198<br>198<br>198                                                         |

| 17.       Low-F         17.1.       II         17.2.       I         17.3.       I         17.3.1.       17.3.2.         17.3.2.       17.3.3.         17.3.4.       17.3.5.         17.3.6.       17.3.7.         17.3.8.       17.4.         17.5.       I                                                                                                                                 | bower timer (LPTIM)<br>httroduction<br>PTIM main features<br>PTIM functional description<br>LPTIM block diagram<br>LPTIM reset and clocks<br>Prescaler<br>Operating mode<br>Register update<br>Timer enable<br>Timer counter reset<br>Debug mode<br>PTIM low-power modes<br>PTIM interrupts                                                                                                                      | 196<br>196<br>196<br>196<br>196<br>196<br>197<br>197<br>197<br>198<br>198<br>198<br>198                                                  |

| 17.       Low-F         17.1.       II         17.2.       I         17.3.       I         17.3.1.       17.3.1.         17.3.2.       17.3.2.         17.3.4.       17.3.5.         17.3.6.       17.3.6.         17.3.8.       17.3.8.         17.4.       I         17.5.       I         17.6.       I                                                                                   | bower timer (LPTIM)<br>Introduction<br>PTIM main features<br>PTIM functional description<br>LPTIM block diagram<br>LPTIM reset and clocks<br>Prescaler<br>Operating mode<br>Register update<br>Timer enable<br>Timer counter reset<br>Debug mode<br>PTIM low-power modes<br>PTIM interrupts<br>PTIM registers                                                                                                    | 196<br>196<br>196<br>196<br>196<br>196<br>197<br>197<br>197<br>198<br>198<br>198<br>198<br>198                                           |

| 17.       Low-F         17.1.       In         17.2.       In         17.3.       In         17.3.1.       In         17.3.1.       In         17.3.2.       In         17.3.3.       In         17.3.4.       In         17.3.5.       In         17.3.6.       In         17.3.7.       In         17.3.8.       In         17.4.       In         17.6.       In         17.6.1.       In | bower timer (LPTIM)<br>httroduction<br>PTIM main features<br>PTIM functional description<br>LPTIM block diagram<br>LPTIM reset and clocks<br>Prescaler<br>Operating mode<br>Register update<br>Timer enable<br>Timer enable<br>Timer counter reset<br>Debug mode<br>PTIM low-power modes<br>PTIM interrupts.<br>PTIM registers<br>LPTIM interrupt and status register (LPTIM_ISR)                                | 196<br>196<br>196<br>196<br>196<br>196<br>197<br>197<br>197<br>197<br>198<br>198<br>198<br>198<br>198<br>199<br>199                      |

| 17.       Low-F         17.1.       II         17.2.       I         17.3.       I         17.3.1.       17.3.1.         17.3.2.       17.3.2.         17.3.3.       17.3.4.         17.3.6.       17.3.6.         17.3.7.       17.3.8.         17.4.       I         17.6.1.       17.6.2.                                                                                                 | bower timer (LPTIM)<br>Introduction<br>PTIM main features<br>PTIM functional description<br>LPTIM block diagram<br>LPTIM reset and clocks.<br>Prescaler<br>Operating mode<br>Register update<br>Timer enable.<br>Timer counter reset<br>Debug mode<br>PTIM low-power modes<br>PTIM interrupts<br>PTIM registers<br>LPTIM interrupt and status register (LPTIM_ISR)<br>LPTIM interrupt clear register (LPTIM_ICR) | 196<br>196<br>196<br>196<br>196<br>196<br>197<br>197<br>197<br>197<br>198<br>198<br>198<br>198<br>198<br>199<br>199<br>199               |

| 17.       Low-F         17.1.       In         17.2.       In         17.3.       In         17.3.1.       In         17.3.1.       In         17.3.2.       In         17.3.3.       In         17.3.4.       In         17.3.5.       In         17.3.6.       In         17.3.7.       In         17.3.8.       In         17.4.       In         17.6.       In         17.6.1.       In | bower timer (LPTIM)<br>httroduction<br>PTIM main features<br>PTIM functional description<br>LPTIM block diagram<br>LPTIM reset and clocks<br>Prescaler<br>Operating mode<br>Register update<br>Timer enable<br>Timer enable<br>Timer counter reset<br>Debug mode<br>PTIM low-power modes<br>PTIM interrupts.<br>PTIM registers<br>LPTIM interrupt and status register (LPTIM_ISR)                                | 196<br>196<br>196<br>196<br>196<br>196<br>197<br>197<br>197<br>198<br>198<br>198<br>198<br>198<br>198<br>198<br>199<br>199<br>199<br>199 |

| 17.6.5   | 5. LPTIM control register (LPTIM_CR)                         | 201 |

|----------|--------------------------------------------------------------|-----|

| 17.6.6   | 6. LPTIM autoreload register (LPTIM_ARR)                     | 201 |

| 17.6.7   | 7. LPTIM counter register (LPTIM_CNT)                        |     |

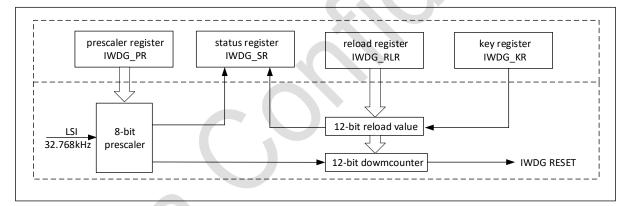

| 18. Ind  | ependent watchdog (IWDG)                                     |     |

| 18.1.    | Introduction                                                 |     |

| 18.2.    | IWDG main features                                           |     |

| 18.3.    | IWDG functional description                                  |     |

| 18.3.1   | . IWDG block diagram                                         |     |

| 18.3.2   | 2. Hardware watchdog                                         |     |

| 18.3.3   | B. Register access protection                                |     |

| 18.3.4   | 5                                                            |     |

| 18.4.    | IWDG registers                                               |     |

| 18.4.1   |                                                              |     |

| 18.4.2   | 1 5 ( = /                                                    |     |

| 18.4.3   |                                                              |     |

| 18.4.4   | 5 ( _ /                                                      |     |

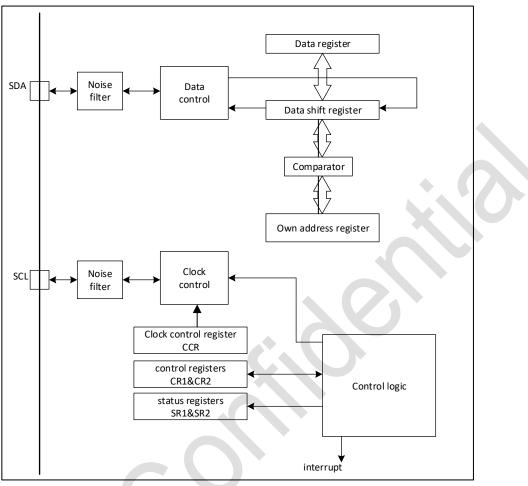

| 19. Inte | er-integrated circuit (I <sup>2</sup> C) interface           |     |

| 19.1.    | Introduction                                                 |     |

| 19.2.    | I <sup>2</sup> C main features                               |     |

| 19.3.    | I <sup>2</sup> C functional description                      |     |

| 19.3.1   | 3                                                            |     |

| 19.3.2   |                                                              |     |

| 19.3.3   |                                                              |     |

| 19.3.4   |                                                              |     |

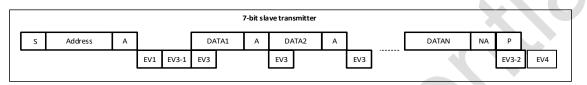

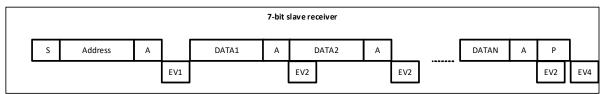

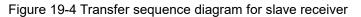

| 19.3.5   | 5. I <sup>2</sup> C master mode                              | 210 |

| 19.3.6   | 6. Error conditions                                          | 215 |

| 19.3.7   |                                                              |     |

| 19.4.    | I <sup>2</sup> C interrupts                                  | 217 |

| 19.5.    | I <sup>2</sup> C registers                                   |     |

|          | . I <sup>2</sup> C control register 1 (I2C_CR1)              |     |

| 19.5.2   |                                                              |     |

| 19.5.3   | <ol> <li>I2C own address register 1 (I2C_OAR1)</li> </ol>    | 219 |

| 19.5.4   | 5 ( _ ,                                                      |     |

| 19.5.5   | , , , , , , , , , , , , , , , , , , ,                        |     |

| 19.5.6   | <b>3 ( 1 )</b>                                               |     |

| 19.5.7   |                                                              |     |

| 19.5.8   | , , , , , , , , , , , , , , , , , , ,                        |     |

| 20. Uni  | versal synchronous asynchronous receiver transmitter (USART) |     |

| 20.1.    | Introduction                                                 |     |

| 20.2.    | USART main features                                          | 224 |

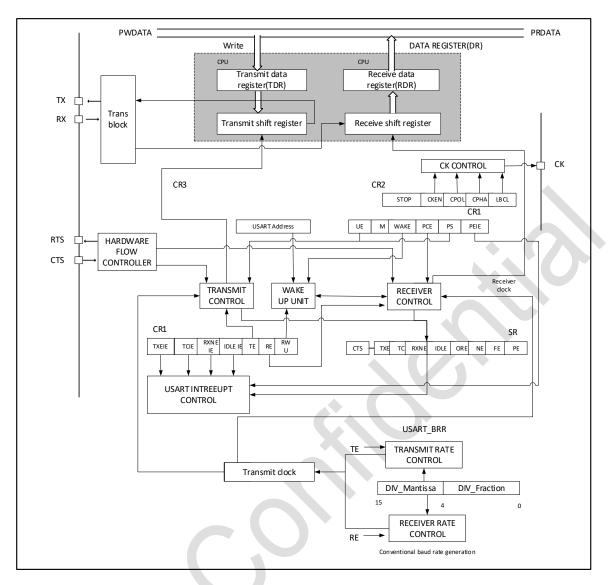

| 20.3.    | USART functional description                       |     |

|----------|----------------------------------------------------|-----|

| 20.3.1.  | USART character description                        | 226 |

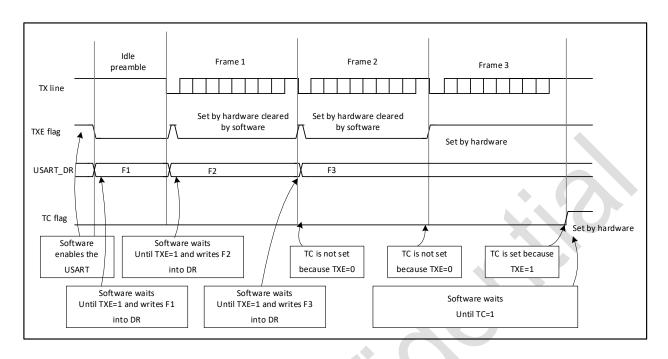

| 20.3.2.  | Transmitter                                        | 227 |

| 20.3.3.  | USART baud rate generation                         | 232 |

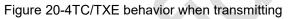

| 20.3.4.  | Tolerance of the USART receiver to clock deviation | 232 |

| 20.3.5.  | USART Auto baud rate detection                     | 233 |

| 20.3.6.  | Multiprocessor communication                       | 234 |

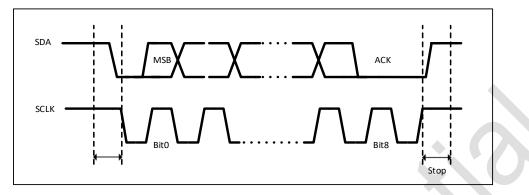

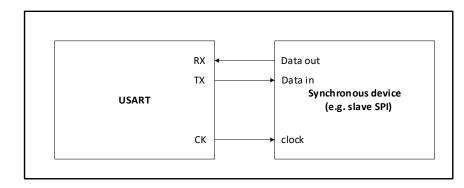

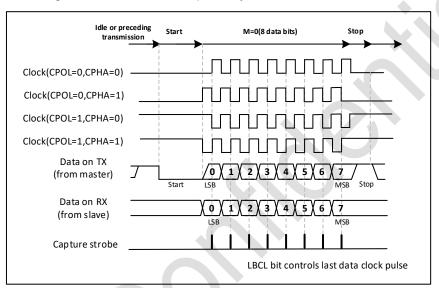

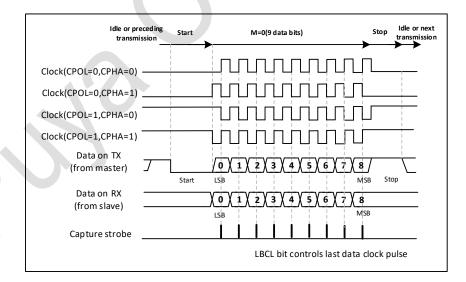

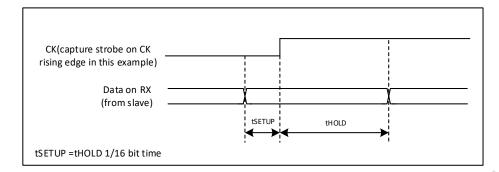

| 20.3.7.  | USART synchronous mode                             | 236 |

| 20.3.8.  | Single-wire Half-duplex communications             | 238 |

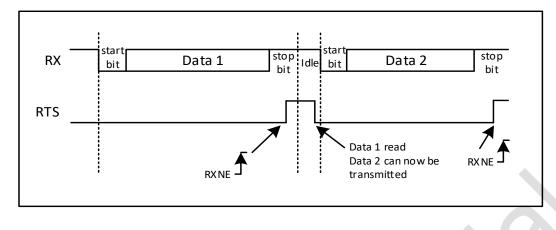

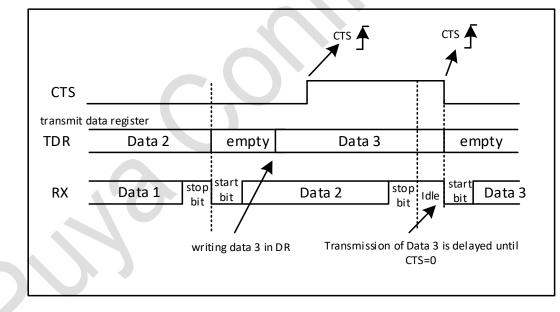

| 20.3.9.  | Hardware flow control                              |     |

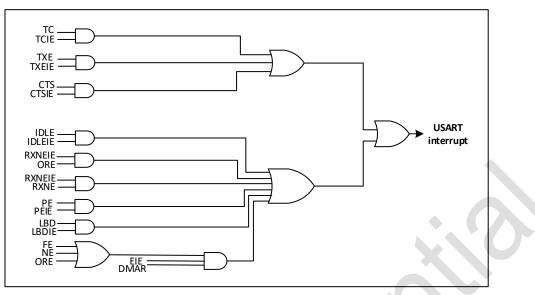

|          | USART interrupt requests                           |     |

| 20.5.    | USART register                                     | 240 |

| 20.5.1.  | USART status register (USART_SR)                   |     |

| 20.5.2.  | USART data register (USART_DR)                     |     |

| 20.5.3.  | Baud rate register (USART_BRR)                     |     |

| 20.5.4.  | USART control register 1 (USART_CR1)               |     |

| 20.5.5.  | USART control register 2 (USART_CR2)               |     |

| 20.5.6.  | USART control register 3 (USART_CR3)               |     |

|          | al peripheral interface (SPI)                      |     |

|          | Introduction                                       |     |

|          | SPI main features                                  |     |

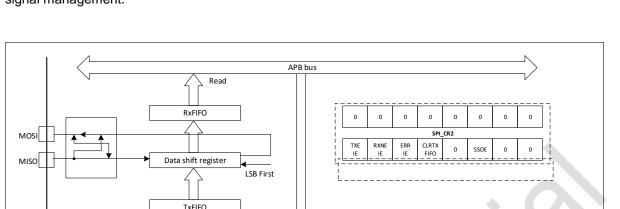

| 21.3.    | SPI functional description                         |     |

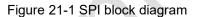

| 21.3.1.  | Overview                                           | 246 |

| 21.3.2.  | Communications between one master and one slave    |     |

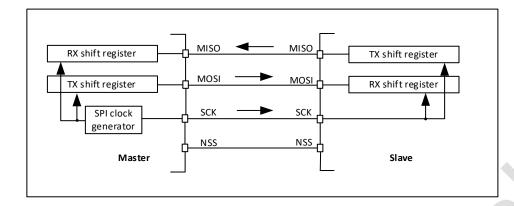

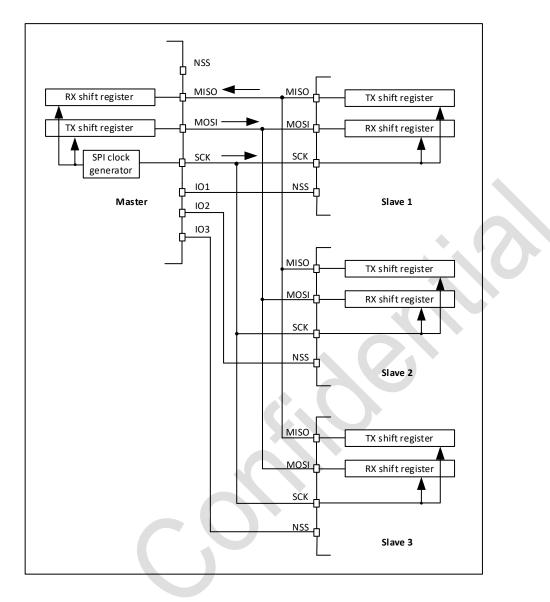

| 21.3.3.  | Multi-slave communication                          | 249 |

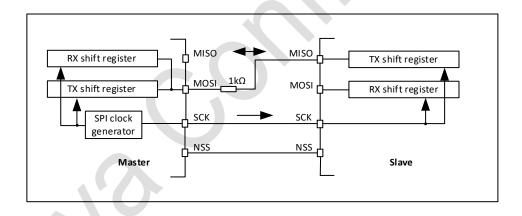

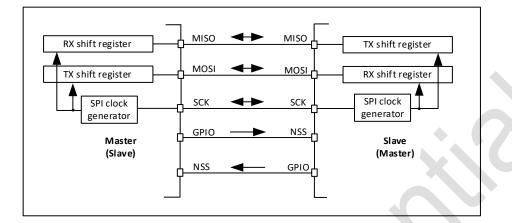

| 21.3.4.  | Multi-master communication                         | 250 |

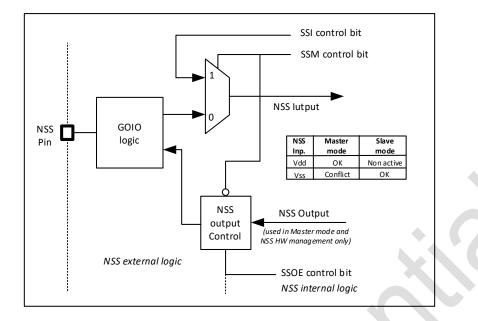

| 21.3.5.  | Slave Select (NSS) pin management                  | 251 |

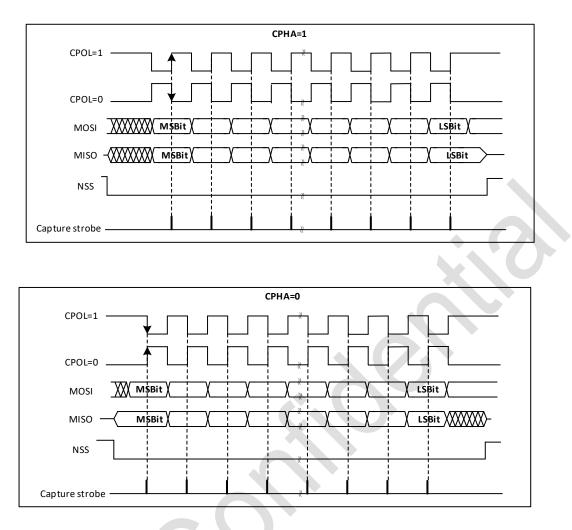

| 21.3.6.  | Communication formats                              | 252 |

| 21.3.7.  | Configuration of SPI                               | 253 |

| 21.3.8.  | Procedure for enabling SPI                         | 254 |

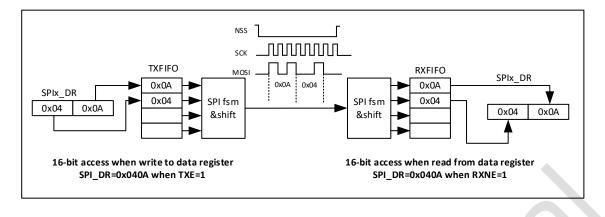

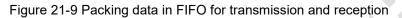

| 21.3.9.  | Data transmission and reception procedures         | 254 |

| 21.3.10  | . SPI status flags                                 | 258 |

| 21.3.11  | Error flags                                        | 259 |

| 21.3.12  | . SPI interrupts                                   |     |

| 21.4.    | SPI register                                       |     |

| 21.4.1.  | SPI control register 1 (SPI_CR1)                   |     |

| 21.4.2.  | SPI control register 2 (SPI_CR2)                   | 261 |

| 21.4.3.  | SPI status register (SPI_SR)                       | 261 |

| 21.4.4.  | SPI data register (SPI_DR)                         |     |

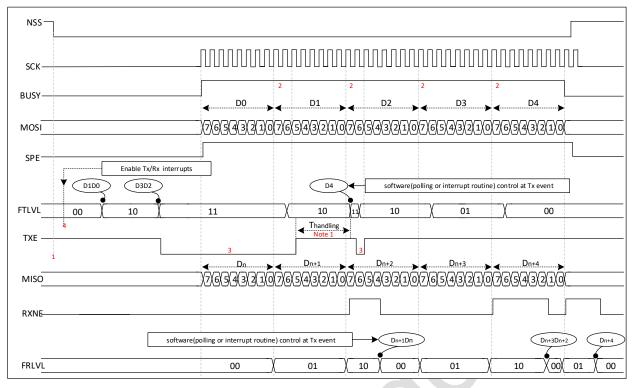

| 22. Debu | ıg support (DBG)                                   |     |

| 22.1.   | Overview                                             |     |

|---------|------------------------------------------------------|-----|

| 22.2.   | Pinout and debug port pins                           |     |

| 22.2.1  | . SWD port                                           |     |

| 22.2.2  | 2. Flexible SWJ-DP pin assignment                    | 264 |

| 22.2.3  | 3. Internal pull-up & pull-down on SWD pins          | 264 |

| 22.3.   | ID codes and locking mechanism                       | 264 |

| 22.4.   | SWD port                                             | 264 |

| 22.4.1  | . SWD protocol introduction                          |     |

| 22.4.2  | 2. SWD protocol introduction                         | 264 |

| 22.4.3  | 8. SW-DP state machine (reset, idle states, ID code) |     |

| 22.4.4  |                                                      |     |

| 22.4.5  | i. SW-DP registers                                   |     |

| 22.4.6  | S. SW-AP registers                                   |     |

| 22.5.   | Core debug                                           |     |

| 22.6.   | Break point unit (BPU)                               |     |

| 22.6.1  | . BPU functionality                                  |     |

| 22.7.   | Data watchpoint trace (DWT)                          |     |

| 22.7.1  | . DWT functionality                                  |     |

| 22.7.2  | 2. DWT Program Counter Sample Register               |     |

| 22.8.   | MCU debug component (DBG)                            |     |

| 22.8.1  | . Debug support for low-power modes                  |     |

| 22.8.2  | 2. Debug support for timers and watchdog             |     |

| 22.9.   | DBG register                                         |     |

| 22.9.1  | . DBG device ID code register (DBG_IDCODE)           |     |

| 22.9.2  | 2. DBG configuration register (DBG_CR)               |     |

| 22.9.3  | B. DBG APB freeze register 1 (DBG_APB_FZ1)           |     |

| 22.9.4  | . DBG APB freeze register 2 (DBG_APB_FZ2)            |     |

| 23. Rev | vision history                                       | 270 |

|         |                                                      |     |

|         |                                                      |     |

5/

## 1. List of abbreviations for registers

| Abbreviation              | Description                                                                                                                 |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------|

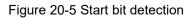

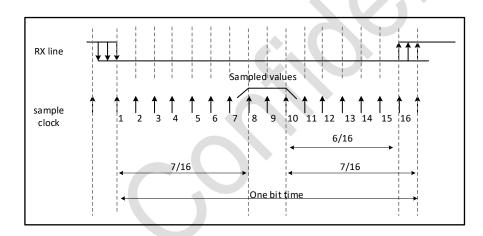

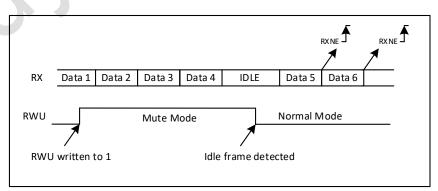

| Read/Write (RW)           | Software can read and write to this bit.                                                                                    |